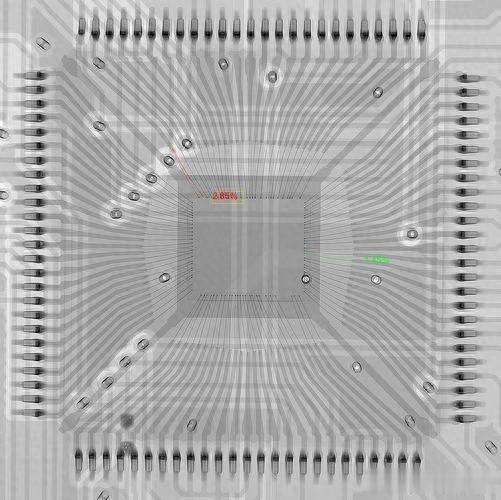

芯片封装失效典型现象

- 2025-07-09 20:09:43

- 487

金线偏移

在封装过程中,金线偏移是较为常见的失效类型。对于 IC 元器件而言,金线偏移量过大可能致使相邻金线相互接触,进而引发短路故障;极端情况下,金线甚至会被冲断,造成断路,使元器件出现缺陷。引发金线偏移的原因复杂多样,具体如下:

树脂流动拖曳力:在填充阶段,若树脂黏性过高、流速过快,产生的拖曳力会作用于金线,导致其偏移量增大,这是金线偏移失效的常见诱因 。

导线架变形:上下模穴中树脂流动波前失衡,会在模流间形成压力差。导线架受此压力差产生弯矩发生变形,由于金线连接于导线架的芯片焊垫与内引脚,导线架变形便会引发金线偏移。

气泡移动影响:填充过程中,空气进入模穴形成小气泡,气泡在模穴内移动时碰撞金线,也会造成金线一定程度的偏移。

保压异常:过保压会使模穴内压力过高,导致偏移的金线无法弹性恢复;迟滞保压则会引起温度上升,对于添加催化剂后反应活跃的树脂,高温使其黏性进一步增加,同样阻碍金线恢复原状。

填充物碰撞:封装材料中添加的填充物,若颗粒尺寸较大(如 2.5 - 250μm),在封装过程中与精细的金线(如 25μm)碰撞,也可能致使金线偏移 。

此外,随着多引脚集成电路的发展,封装内金线数量与引脚数目不断增加,金线密度随之提升,这也使得金线偏移现象更为显著。为有效减少金线偏移,防范短路或断路问题,封装工程师需审慎选择封装材料,精准调控工艺参数,降低模穴内金线所受应力,避免出现过大的偏移量。

芯片开裂

IC 裸芯片的制造原料通常为单晶硅,这种材料虽具备高强度,却因脆性大的特性,在遭受外力作用或表面存在瑕疵时,极容易出现破裂情况。在晶圆减薄、晶圆切割、芯片贴装和引线键合等一系列需要施加应力的工艺操作过程中,芯片开裂的风险大幅增加,这一问题已成为致使 IC 封装失效的重要因素之一。若芯片裂纹未蔓延至引线区域,通过常规手段很难发现;更有部分存在裂纹的芯片,在常规工艺检查与电学性能检测时,其性能表现与正常芯片并无明显差异,使得裂纹问题极易被忽略。然而,这些隐藏的裂纹会对封装后器件的稳定性与使用寿命造成严重威胁。由于常规电学性能测试无法有效识别芯片开裂,因此需要借助高低温热循环实验进行检测。该实验利用不同材料热膨胀系数的差异,在加热和冷却交替过程中,材料间产生的热应力会促使裂纹逐步扩展,直至芯片彻底破裂,最终在电学性能上呈现出异常状态。

鉴于外部应力是引发芯片开裂的主因,一旦检测到芯片存在裂纹,就必须立即对芯片封装的工艺流程和参数进行优化,最大程度减少工艺环节对芯片产生的应力影响。例如,在晶圆减薄工序中,采用更为精细的加工方式,提高芯片表面的平整度,以此消除潜在应力;晶圆切割时,运用激光切割技术替代传统方法,降低切割过程对芯片表面造成的应力损伤;在引线键合环节,精准调控键合温度和压力参数,确保键合过程平稳安全。

界面开裂

开裂问题不仅存在于芯片内部,在不同材料的交界位置同样会出现,这种现象被称为界面开裂。在界面开裂的初始阶段,各部件之间的电气连接尚能维持正常,但随着使用时间的延长,热应力的持续作用以及电化学腐蚀的影响,会导致界面开裂程度不断加剧,最终破坏部件间的电气连通性,对集成电路的可靠性产生严重影响。封装过程中应力过大、封装材料受到污染等工艺缺陷,是引发界面开裂的主要根源。界面开裂可能出现在金线与焊盘的连接部位,造成电路断路故障;也可能发生在外部塑料封装体中,降低封装对芯片的防护性能,导致芯片受到污染。因此,必须采用专业的检测方法对潜在的界面开裂问题进行全面排查,并根据检测结果对工艺方案进行针对性调整 。

基板裂纹

在倒装焊工艺里,通过焊球实现芯片与基板焊盘的电气连接,而在此过程中,基板开裂是较为常见的失效模式,在引线键合环节同样可能出现此类问题。基板一旦开裂,会严重干扰芯片正常的电学性能,引发断路、高阻抗等故障,影响集成电路的整体功能。

基板开裂的成因较为复杂,一方面,芯片或基板本身若存在材料缺陷、内部应力集中等问题,会降低其结构强度;另一方面,焊接过程中的工艺参数匹配不当也是关键因素。例如,键合力过大、基板温度控制不合理、超声功率设置不精准等,都会使基板承受额外应力,进而导致裂纹产生 。

再流焊缺陷

晶圆翘曲

再流焊工艺容易引发晶圆翘曲问题。由于封装体由多种材料构成,各材料热膨胀系数存在差异,同时还受流动应力和黏着力影响,在封装过程中外界温度变化时,封装体内部会产生内应力,而翘曲变形便是材料释放内应力的一种表现形式,这种现象在再流焊接阶段尤为突出。翘曲受多个工艺参数协同作用,通过针对性调整部分参数,能够有效缓解或消除这一问题。

器件受力不均衡是导致翘曲的主要根源。在预热阶段,因材料热膨胀系数不匹配、焊膏涂覆不均或器件放置偏差等原因,器件一端可能脱离焊膏,阻碍热量正常传导。当热量经器件传导时,一端先熔化的焊料会形成新月形,其表面张力产生的旋转力矩大于器件自身重力,从而致使器件发生翘曲变形。

为改善晶圆翘曲状况,可从多方面着手优化工艺:首先,要严格把控焊膏印刷与器件放置精度,规范设备操作流程,定期维护印刷和安装设备,确保生产过程稳定;其次,重视印刷清晰度与精确度控制,这直接关系到衬垫配置,若控制不当会加剧器件两端受力失衡,需定期检查印刷配准参数,及时修正偏差,清洁印刷模板防止堵塞,同时保证焊膏湿度适宜,支撑基板平整坚固;最后,关注器件放置环节,定期校准进料器位置,精准控制放置对准,降低放置速度,合理选择拾取工具喷嘴尺寸,并确保支撑平台平稳可靠。

此外,焊接材料和印刷电路板特性也会对翘曲产生影响。焊接合金熔点时的表面张力大小,与翘曲时的扭曲力呈正相关,虽目前尚无统一的合金标准评估体系,但部分厂商尝试使用 Sn/Pb/In 合金,发现对翘曲有一定抑制作用,但效果有限。不同类型焊膏的特性差异,会改变其对器件的作用效果,焊膏活性越强,越易引发翘曲;印刷电路板和器件表面的光洁度,会影响焊膏湿润性能,过量使用焊膏会增加熔化时的应力,适当减少用量有助于降低翘曲风险。在再流焊过程中,若器件两端热传递速率差异显著,也会因受力不均导致翘曲现象发生 。

锡珠

在再流焊工艺中,锡珠是一种常见的缺陷类型,多聚集于无引脚片式元器件两侧。若锡珠未与其他焊点相连,不仅会影响封装外观,还可能干扰产品电性能。锡珠产生的原因涵盖多个方面,涉及模板设计、印刷操作、锡膏使用及工艺参数设置等环节。

从模板开口角度来看,若钢网开口尺寸过大,或开口形状与元器件、焊盘不匹配,在贴装片式元器件时,焊膏易溢出焊盘范围,进而形成锡珠。为规避此问题,片式阻容元器件的模板开口尺寸通常应略小于印制板焊盘。考虑到线路板刻蚀因素,一般将焊盘的模板开口设置为印制板焊盘尺寸的 90% - 95%,同时还需依据实际生产情况灵活选择合适的开口形状,以此减少焊膏过量挤出的风险。

模板与印刷电路板的精准对位及稳固固定同样关键。对位偏差会致使焊膏蔓延至焊盘外,增加锡珠产生几率。印刷锡膏的方式包括手工、半自动和全自动,即便在全自动印刷模式下,压力、速度、间隙等参数仍依赖人工设定。因此,无论采用何种印刷方式,都需协调好机器、模板、印刷电路板和刮刀之间的关系,确保印刷质量稳定。在锡膏使用方面,从冷藏室取出的锡膏若升温时间不足、搅拌不均匀,容易吸湿。在高温再流焊过程中,锡膏内水汽挥发,就会形成锡珠。所以,使用前应将锡膏在室温下放置约 4 小时恢复温度,并充分搅拌均匀 。

温度曲线作为再流焊工艺的核心参数,包含预热、保温、回流、冷却四个阶段。预热和保温环节能够降低元器件与印刷电路板所受热冲击,促使锡膏中溶剂充分挥发。若预热温度不足或保温时间过短,将直接影响焊接质量,通常建议保温阶段控制在 150 - 160℃、持续 70 - 90 秒。此外,生产中若需重新印刷锡膏,务必彻底清理残留锡膏,防止其形成锡珠,清理时应避免锡膏流入插孔造成通孔堵塞 。

空洞

空洞也是再流焊的主要缺陷之一,表现为焊点表面或内部存在气孔、针孔。其形成原因多样:焊膏中金属粉末含氧量过高、使用回收焊膏、工艺环境差混入杂质等,需严格把控焊膏质量;焊膏受潮吸收水汽,可通过控制环境温度在 20 - 26℃、相对湿度 40% - 70%,且待焊膏达室温后再开盖使用来解决;元件焊端、引脚、印制电路板焊盘氧化污染或印制板受潮,应遵循元件先进先出原则,避免在潮湿环境存放并注意使用期限;升温速率过快导致焊膏中溶剂和气体未充分挥发,可将 160℃前的升温速率控制在 1 - 2℃/s。

再流焊过程中还存在多种其他缺陷。例如,焊膏熔融不完全,表现为焊点周围部分或全部焊膏未熔化;湿润不良,即元件焊端、引脚或焊盘出现不沾锡或局部不沾锡现象;焊料量不足,焊点高度未达规定标准,影响焊点机械强度与电气连接可靠性,甚至引发虚焊、断路;桥连(短路),元件端头、引脚或与邻近导线间出现不应有的焊锡连接;锡点高度异常,焊料向焊端或引脚根部迁移,高度触及或超过元件体;锡丝,元件焊端、引脚间或与通孔间存在细微锡丝;元件或端头出现裂纹、缺损;元件端头电极镀层剥落;冷焊(焊锡紊乱),焊点表面有焊锡紊乱痕迹;焊点表面或内部出现裂缝等。还有一些肉眼难以察觉的缺陷,如焊点晶粒大小、内部应力、内部裂纹等,需借助 X 射线检测、焊点疲劳测试等手段才能发现 。

来源于学习那些事,作者前路漫漫

- 上一篇:女子给自己签字开了小时无痛

- 下一篇:洛杉矶